이번에는 캐시 일관성 에 대해 알아보자.

캐시 일관성이란 멀티코어 프로세싱에서 자주 등장하는 개념인데, 한마디로 말해 여러 캐시의, 즉 하나 이상의 캐시의 데이터 불일치를 나타내는 용어이다.

예를 한번 들어보자.

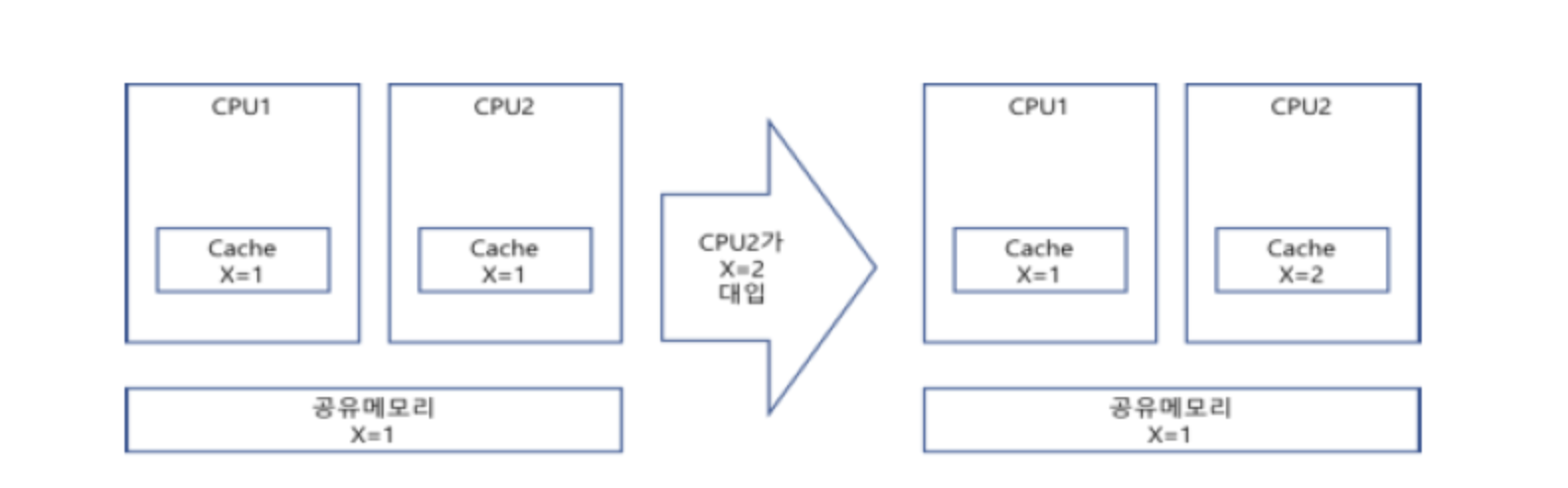

위의 예시는 두개의 코어가 있다고 가정한다.

예를 들어, 메모리 주소 0x1234ABCD에 X = 1이라는 데이터가 있다고 해보자.

그 다음, CPU1에서 0x1234ABCD에 저장되어 있는 X변수를 읽어오고싶다고 해보자. 그러면 1이 읽힐 것이다. 그러면 이제 CPU2에서 같은 주소로 내려가 X를 읽는다고 해보자. 그러면 버스에서는 메인 메모리의 0x1234ABCD에 있는 X에 접근하여 1을 읽어올것이다. 이 상황에서는 문제가 없다.

하지만,

CPU2에서 이제 X에 1 대신 2를 쓴다고 해보자. 이렇게 되면, CPU1과 CPU2가 바라보는 X값은 다를 것이다. 즉, 어떤 값이 유효한 값인지 알 수 없다.

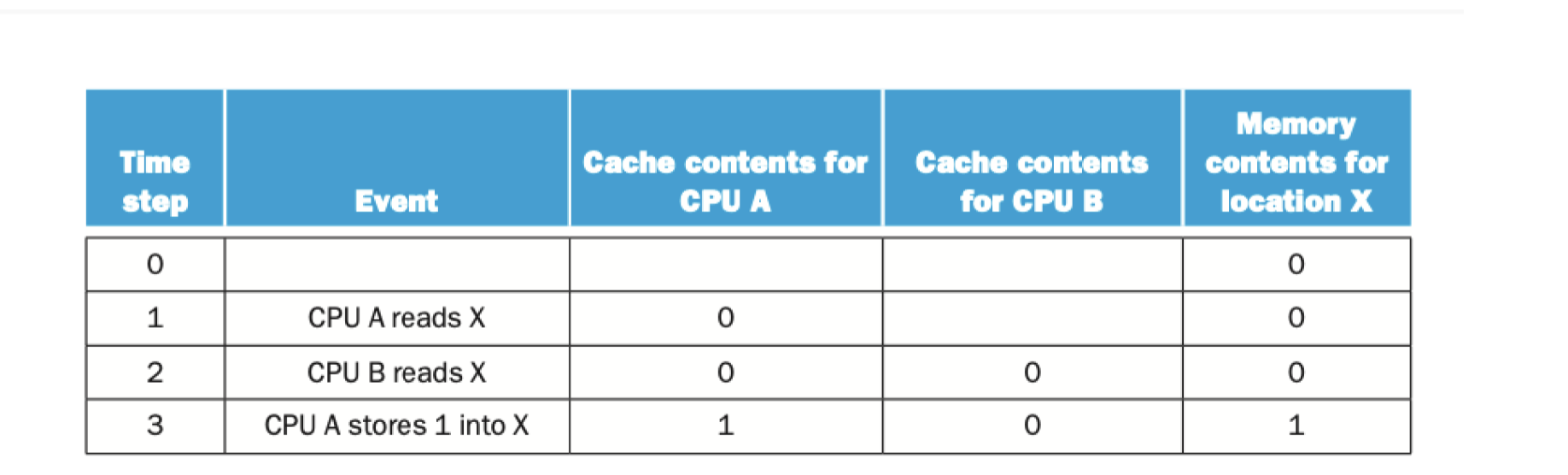

위 그림이 이해가 안된다면 아래는 캐시 일관성 문제를 표현한 테이블이다.

맨 왼쪽 열에 있는 Time step은 동작이 수행되는 과정을 시간별로 분류한것이다.

0. X에는 0이라는 정수가 존재한다.

1. CPU A는 X값을 메모리에서 읽어온다 => 0을 읽어와 캐시에 저장할것이다.

2. CPU B도 X값을 메모리에서 읽어온다 => 0을 읽어와 캐시에 저장할것이다.

(이 시점에서 두개의 캐시 A,B에는 각각 X에서 읽어온 0이라는 값이 저장된다.)

3. CPU A는 X값을 1로 바꾼다. 이때, 메모리에서 X는 1을 가지고 있다.

같은 문제가 발생한다. 어느 캐시에 있는 X값이 올바른 X값일까?

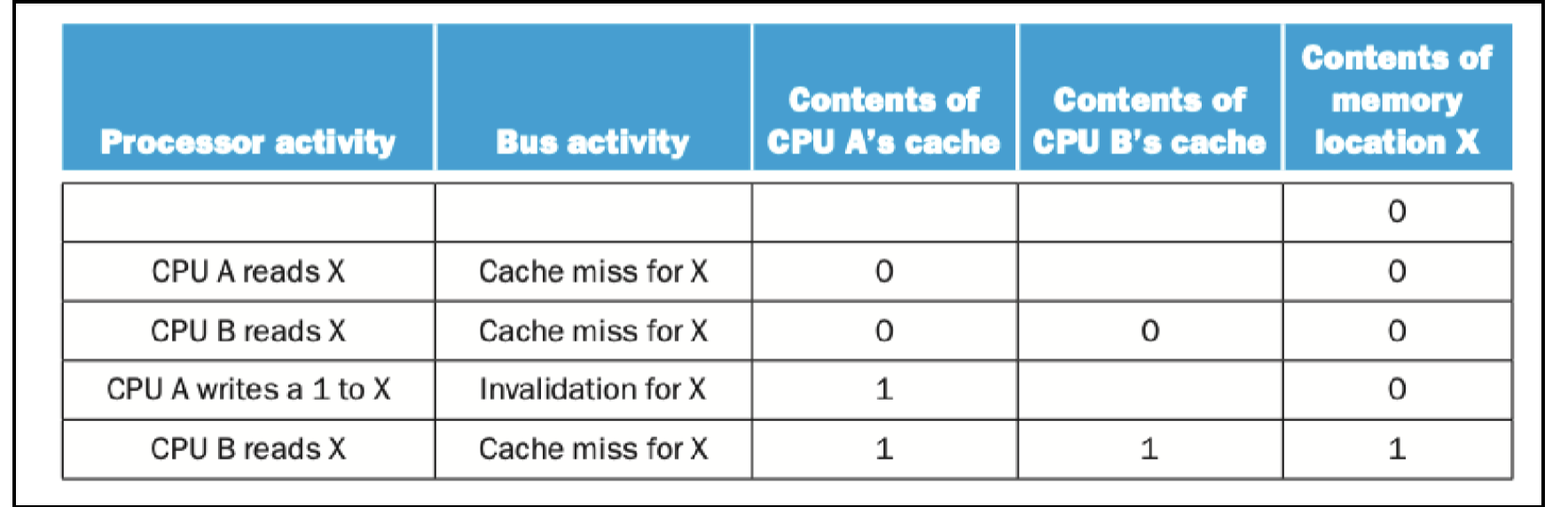

여기서 일관성 문제를 해결하기 위해 아래 세가지 상태변수가 등장한다.

- Invalid[0]

- Shared[1]

- Exclusive[1]

※Invalid : 여러개의 프로세서중 하나의 프로세서에서 어느 한 메모리 주소에 "쓰기" 요청을 할때, 현재 쓰기 요청을 하는 프로세서를 제외한 모든 프로세서를 invalid(무효화) 하게 만드는것이다. 예를 들어, 위의 예시에서 CPU A가 X에 쓰기 요청을 한다면, A는 버스를 통해 다른 프로세서들에게 "내가 지금 X값을 변경하고 있으니 너희 나머지 모두들의 X값을 무효화 시킬게. 만약 너가 X를 바꾸거나 읽고 싶다면, 다시 메인 메모리로 돌아가 업데이트된 X값을 가져와서 처리해" 라는 동작이다. [쓰기 전용]

※ Exclusive : 위의 예시에서, 이제 A를 제외한 다른 프로세서들은 모두 invalid상태에 머물러 있다. 그렇다면 A는 무슨 상태일까? A는 여기서 Exclusive(독점적인) 상태이다. "오직" A만이 X의 값을 변경하거나 읽을 수 있는 상태라는 말이다.

※ Shared : invalid나 Exclusive한 상태가 아닌 상태이며, "안전하게" 즉, 캐시 블럭을 문제 앖이 읽어올수 있다는 뜻이다. [읽기 전용]

예시를 들어보자.

1. 메모리의 X에는 0이라는 정수가 저장되어 있다.

2. A가 X를 읽어온다(캐시에는 아무것도 없는 상태이므로 캐시 미스 발생), 0을 읽어와 캐시에 저장한다.

3. B가 X를 읽어온다(캐시에는 아무것도 없는 상태이므로 캐시 미스 발생), 0을 읽어와 캐시에 저장한다.

4. A는 X에 원래 있던 0이라는 값 대신 1을 쓴다(이 시점에서 A는 Exclusive를 가지고, 캐시 B에 있던 X값(0)은 무효화(invalidate)된다).

5.B가 이제 X를 읽어온다. 그러면 B는 업데이트 된 1을 제대로 읽어올것이다.(이때, Exclusive했던 A는 더이상 Exclusive하지 않게 된다.)

'컴퓨터 구조 + 운영체제(OS)' 카테고리의 다른 글

| [OS]프로세스 상태와 계층구조 (1) | 2024.02.01 |

|---|---|

| 운영체제 pt 1. 운영체제(Operating System)의 기초(System call) (0) | 2024.01.18 |

| 병렬 컴퓨팅(Parallel Computing) (0) | 2023.12.04 |

| 가상 메모리(Virtual Memory)와 TLB 의 개념 (1) | 2023.11.30 |

| 컴퓨터 캐시의 동작 과정 (0) | 2023.11.29 |